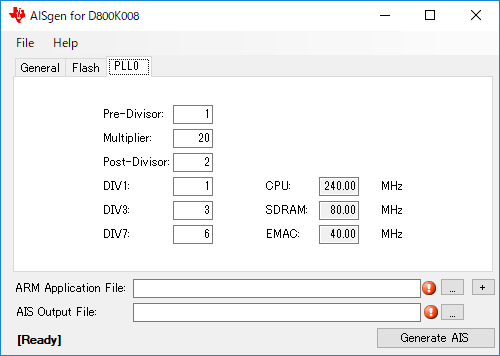

AM1806: What's "EMAC" on AISgen tool

TDA4VM SOM Layout questions

Couple questions from one of my customers regarding the layout of the TDA4/J7 EVM:

- There is a desire to avoid editing the high speed signals in the board layout, but it was noted that there are some uncommon callouts. Single-ended (33, 40 and 66 ohm) and differential (66, 80, and 132 ohm) signals. Here are some examples:

- 33 ohm single-ended: LPDDR4_CAx nets on Layer 1 and Layer 7. It’s also on the SI simulation coupon.

- 40 ohm single-ended: LPDDR4_DQx nets on Layer 3 and Layer 5. It’s also on the SI simulation coupon.

- 66 ohm single-ended: LPDDR4_CAx nets on Layer 3. It’s also on the SI simulation coupon.

- DDR_CK diff pair appears to be 66 ohms differential on Layer 7, and 132 ohms differential on Layer 3.

Question 1: Were these DDR signal callouts determined by simulation?

Question 2: What material was used and is there a reference stackup doc from the manufacturer? Since the fastest speeds in the design will likely be on CSI and PCIe (Gen 4) the customer wants to make sure that the materials will meet the speed requirements.

Thanks

John

AM5746: SDK questions

Part Number: AM5746

Hi,

My customer is interested in AM5746 as they need EMIF ECC.

Questions:

Q1) Does Processor SDK (RTOS and Linux) support EMIF ECC feature?

Q2) Customer needs total three Ethernet ports, so PRU-ICSS EMAC will be used.

It seems current SDK does not support PRU-ICSS EMAC on IDK574x.

When it will be supported (both RTOS and Linux)?

Thanks and regards,

Koichiro Tashiro

AM4376: Ethernet Transmit DMA fails sometimes with error "Ownership bit not set in SOP buffer"

Part Number: AM4376

I am writing a driver for the AM4376 Ethernet sub-system. My DMA engine stops sometimes with register CPSW_DMASTS == 0x00200000 = TX_HOST_ERR_CODE == 0010 = "Ownership bit not set in SOP buffer". I understand what this means and I am certain that I am setting the SOP and Ownership bits in the appropriate TX buffer descriptor. I am wondering if there are some timing issues between writing the descriptor and starting the DMA engine. Also are there any special timing issues recovering from a misqueued packet? Is there anything I can do or wait for to make sure the descriptor data I push out is actually visible to the DMA engine? The descriptors are in a part of memory that is not cached, so that should not be the problem.

Any advice would be appreciated.

Thanks

Cliff

Looking for help on choosing MCU for designing an industrial heating controller.

Hi everybody,

I'm Datïan. I'm going to design a MCU based device via SSRs (Solid State Relay) to control multiple channel of AC 220V load which heats some kind of fluid material. The operation temperature is from -58 oF to 572 oF ( -30 oC to 300 oC). Could you give some advice on choosing the type of controller and SSR?

Best regards

Datïan

2019.08.23

TDA2SX: the format of display bubffer ,can you explain?

Part Number: TDA2SX

displayLink_drv.c

we dump the display buffers, and play the file ,we found that some buffer was RGB32, some buffer was YUYV, i don't know why?

the detail folows:

Int32 DisplayLink_drvProcessData(DisplayLink_Obj *pObj)

Vps_printf(" zhoule pFrame address 00 %p %p %d\n",pFrame->addr[0U][0U],pFrame->addr[1U][0U]);

then we used the address for dump, there were seiral buffers for display.

./devmsave 0xa0984000 0x1c2000 dump.txt

then play the dump.txt, some address the format was RGB32 ,some was YUYV,why?

specificly, when pFrame->addr[0U][1U] was null , the format was YUYV

AM5728: _

PROCESSOR-SDK-AM437X: Enable PRU-ICSS Hardware Uart

Part Number: PROCESSOR-SDK-AM437X

Hello,

I currently need to enable the PRU-ICSS hardware uart by the official example, am437x/PRU_Hardware_UART. The uart pins are J16-28 for UART RX and J16-30 for UART TX. ARM core runs the Linux PREEMPT_RT. The following snip shows how I start this PRU-ICSS firmware:

# echo stop > /sys/class/remoteproc/remoteproc1/state # echo PRU_Hardware_UART.out > /sys/class/remoteproc/remoteproc1/firmware # echo start > /sys/class/remoteproc/remoteproc1/state # cat /sys/class/remoteproc/remoteproc1/firmware PRU_Hardware_UART.out # cat /sys/class/remoteproc/remoteproc1/state running

However, there is nothing from UART TX. Is there anything needs to change in the device tree?

Thanks,

Regards,

George Kang

AM5728: Linux/AM5728: Camera sensor issue

AM6548: secure boot and eFuse usage

Part Number: AM6548

I have a AM65x EVM board. I want to develop secure boot by optee. i have some questions following :

1. how about the develop steps for secure boot feature in this board ?

2. how to write key in eFuse ?

3. how to write key in development status, you know the eFuse just can write one time, but I will write many times key in development status

4. secure boot is singed the firmware or encrypt firmware ?

AM3359: FSoE support on Sitara devices

Part Number: AM3359

Hi,

I am interested in Safety over EtherCAT(FSoE) and would like to implement it with Sitara.

I think that the current TI Processor SDK NOT support FSoE, Does anyone know third parties that can support FSoE?

Is there any information on the implementation of FSoE in Sitara products?

Best Regards,

H.U

CCS/AM5718: AM5718 Boot from NOR

Part Number: AM5718

Tool/software: Code Composer Studio

Hi,

One of our customer using AM5718 MPU for WiFi streaming video application.

They have some query below...

1. Processor AM5718 is having MMC1 to MMC4 for connecting all type memory peripherals like SD CARD or eMMC Flash or SDIO CARD. In Our schematics we have connected MMC4 signals for SD Card connection and QSPI1 signals for NOR Flash(512 mb). For processor booting we have done SYSBOOT registers settings for NOR Flash and we tried booting but not able to boot processor. Can you help us to get procedure how we can boot from NOR Flash.

2. In AM5718 EVM, SD Card signals are connected to MMC1 for processor booting from sd card. We have connected to MMC4 because in PINMUX file of AM5718, if we configure MMC1 as SD Card it is showing voltage constraint issue. So we have connected to MMC4 and we have done required changes of SYSBOOT setting for SD Card booting but we found that Processor not booting again. So is it possible to boot SD card by connecting it to MMC4 or compulsory we need to use MMC1 for SD Card connection.

3. In MMC1 signals for SD CARD connection there is one pin called MMC1_SDCD is this pin is compulsory required for SD card detection for Processor to boot.

Please help to resolve...

Regards,

Muthu S

AM6548: efficient use of NAVSS in TI-RTOS

Part Number: AM6548

Dear Champs,

For AM65x NAVSS, could you please guide me how customer can achieve maximum throughput using TI-RTOS SDK using NAVSS?

Is there any usecase or example in the TI-RTOS SDK?

Thanks and Best Regards,

SI.

Compiler/AM3352: U-boot recovery image

Part Number: AM3352

Tool/software: TI C/C++ Compiler

Hi,

I want to generate recovery image to get uboot# prompt for boot-loader version u-boot-2014.07-g7e537bf.

Please let us know how to generate recovery image for above version to my custom board.

I am able to generate u-boot.bin but don't know how to generate recovery images(u-boot-spl.bin and u-boot_uartboot.img(MLO)).

Please help me to generate recovery image.

Thanks and Regards,

Subramanya

TMS320C5517: McSPI usage

Part Number: TMS320C5517

Hi Champs,

1:Could you please tell us how to reset McSPI_CLK bit count automatically when assert McSPI_CS0 ?

2:When McSPI_CS0 became negate statement during data transmit , does C5000 has any trigger or flag ?

For example, some of other vendor MCU have "error interrupt " when CS0 negate during data transmit.

Regards,

Kz777

TMDSIDK574: GMAC_SW interrupt pacing

Part Number: TMDSIDK574

Hi TI,

refrerring to TRM AM5748, section 24.12.4.5.5 Interrupt Pacing:

For a test, I set rx_pacing to 500us: ethtool -C eth0 rx-usecs 500.

I'm using Linux SDK5.3. Driver sets INT_PRESCALE and WR_C0_RX_IMAX as expected:

WR_INT_CONTROL Read at address 0x4848520C : 0x003F01F4

--> pacing is enabled

--> INT_PRESCALE = 1F4h = 500d, 500 x GMAC_MAIN_CLK^-1 (125MHz) = 4us

WR_C0_RX_IMAX: Read at address 0x48485270 (0xb6f92270): 0x00000002 --> 2 interrupts per 1ms, as expected. This is intr_max

"The interrupt pacing module counts the number of interrupts that occur over a 1 ms interval of time.". Let's assume I get 10 rx ints per ms

-> intr_cnt = 10

If we look a the algorithm

if (intr_count > 2*intr_max)

pace_timer = 255;

else ...

Or

if (10 > 4)

pace_timer = 255;

else ...

The way I understand the algo is:

- interrupts are (always) suppressed for 255*4 = about 1ms

- always the first "if" is taken, so we get and interrputs every second

In reality I get an int every 500us.

So it seems I do not fully understand the algorithm or is it not properly documented?

Best regards, Chris

TDA3LX: Reset not releasing for the DSP

Part Number: TDA3LX

Hi,

I am following the reset sequence for DSP1 & DSP2 as mentioned in TRM 3.5.6.2 DSP1 Subsystem Software Warm Reset Sequence page no.351.

I am trying to assert the global and local reset for DSP1 & DSP2. The values are also updating in the RM_DSP1_RSTCTRL(0x4AE0 6410) register. But reset status is not updating in status register RM_DSP1_RSTST(0x4AE0 6414) register. Same thing i tried for EVE core then it is updating correctly. Please let me know if something is wrong or any other case i need to check.BR,

Sagar

AM3359: SPI flash example

Part Number: AM3359

Hello, TI Experts,

Our customer sent us a question about "SPI-Flash read/write" with PROCESSOR-SDK-RTOS-AM335x with TMDSICE3359.

They want to know how to create the code for SPI-Flash read/write on the TMDSICE3359.

Question:

- Are there any sample code such as CCS sample project for SPI-Flash read/write on the TMDSICE3359?

We would appreciate if you tell us the recommended way to create the code for SPI-Flash read/write on the TMDSICE3359.

Best regards,

[TDA4M]AR0233 camera sensor bring up

Hi,

I tried to bring up AR0233 on TDA4EVM board with Fusion board (Rev-B) on PSDKRA-09.00

There is no interrupt reached after the initialization (ub960-ub953-ar0233).

I have checked the status of ar0233 and ub960, the frame count increased. After measured the clock lane and data lane of UB960. There are CSI signal output on oscilloscope.

attched file is the debug patch and log file please help to check and give suggestions.

Regards

Joe(Please visit the site to view this file)

AM3354: How do I Access PMIC(TPS65910) registers over i2c?

Part Number: AM3354

Dear TI Team,

We would like to read/write TPS65910 registers over i2c0? Can you pls. suggest us how can we do this?

Regards,

Zafer Çalışkan