Hi:

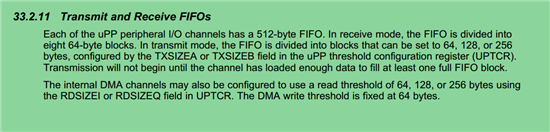

As picture described ,each UPPperipheral I/Ochannel has a 512 byte FIFO,When in transmit mode ,Transimssion will not begin until the channel has loaded enough data to fill at least one full FIFO,But when received,not give described.My question is :

(1):Does it means when i set the RDSIZEI to 0x03 in UPTCR register,it will read data out only when 256 byte had loaded into the receive FIFO?

(2):Does it means the number when i send or received must be integer multiples of 64 byte?

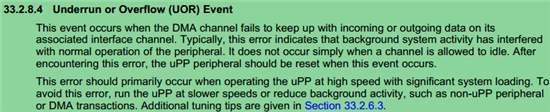

Another question is I used EDMA to read or write data with NAND, also i used UPP to read data from FPGA,the speed is 25MHz,but when i using ,i find the underrun or overflow event, as described as datasheet:

the speed about the UPP is not fast enough,so i guess it may be the reason about EDMA i used to caused the UOR event,How can i solved this question?Improve the priorit about UPP from 4 to 0?or change the value about the SDMAARBE or MDMAARBE in EMC block?

Thank you