In our design we use AM1808 and FPGA. FPGA is configured and data are transferred through uPP peripheral. We use Linux as operating system, and uPP driver based on TI's provided BIOS/CSL driver.

uPP operate in two modes:

1. Data mode, where data from FPGA are transferred by Channel A (Channel A is configured as INPUT) and data to FPGA are transferred by Channel B (B is OUTPUT).

2. Configuration mode, for FPGA content load, where Channel A is OUTPUT, and Channel B is configured as INPUT.

Sometimes we need to change FPGA content. Then we change uPP interface configuration, load new FPGA content, and change interface back. It works fine until we do not read from FPGA (in Data mode) before uPP reconfiguration. If we do read before reconfiguration, then FPGA content load fail, because uPP do not send correct data to Channel A. It seems like first 64 bytes of programmed DMA transfer disappear (uPP START signal is generated properly, but in wrong place?). We have captured uPP registers logs in time of DMA transfer programming, and registers content is same for both case (OK and Fail). In time of reconfiguration uPP peripheral software reset is performed (we test also reset uPP multiple times). Could someone, please, suggest what's wrong?

Regards,

Slavomir

Some details:

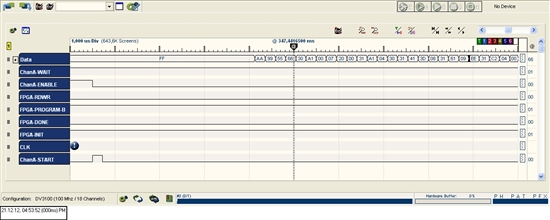

Here is a picture with correct data sent. Couple of 0xFF at beginnig followed 0xAA 0x99... uPP channel A is configured as output. Channel B configured as input (tested also as uncofigured - no matter).

From logs - printed part of buffer content - address 0xc5d00000:

0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff

0xaa 0x99 0x55 0x66 0x30 0xa1 0x00 0x07 0x20 0x00 0x31 0xa1 0x04 0x30 0x31 0x41

0x3d 0x08 0x31 0x61 0x09 0xee 0x31 0xc2 0x04 0x00 0x20 0x93 0x30 0xe1 0x00 0xcf

0x30 0xc1 0x00 0x81 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00

and values writed to uPP registers:

window: 0xc5d00000

line|bytes: 0x000e7ff8

offset: 0x00007ff8

Then we reconfigure uPP interface to ChA as input, ChB as output, send and read some data to/from FPGA. Read is impotrant. Without read everything work OK.

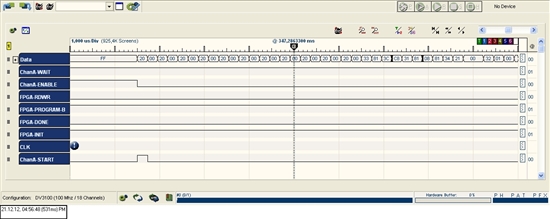

In time, when FPGA content need to be changed uPP interface is reconfigured to "configuration mode ", and data are sent (for this case data are same).

Part of interface reconfiguration is also sw reset of uPP peripheral.

Printed buffer content is same - buffer address 0xc5d00000:

0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff 0xff

0xaa 0x99 0x55 0x66 0x30 0xa1 0x00 0x07 0x20 0x00 0x31 0xa1 0x04 0x30 0x31 0x41

0x3d 0x08 0x31 0x61 0x09 0xee 0x31 0xc2 0x04 0x00 0x20 0x93 0x30 0xe1 0x00 0xcf

0x30 0xc1 0x00 0x81 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00 0x20 0x00

and data to DMA registers are also same

window: 0xc5d00000

line|bytes: 0x000e7ff8

offset: 0x00007ff8

But uPP send wrong data. First 64 bytes are missing.